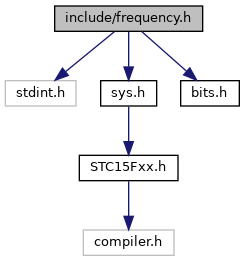

Include dependency graph for frequency.h:

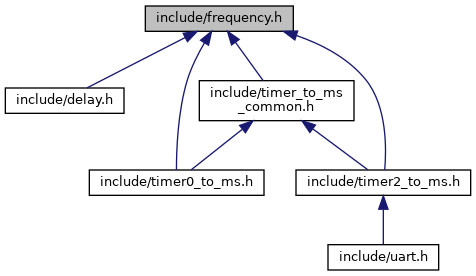

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | get_master_clock_frequency() (MAIN_Fosc) |

| Get MAIN_Fosc value. | |

| #define | get_master_clock_frequency_high_part() (MAIN_FoscH) |

| Get high part of MAIN_Fosc defined as MAIN_FoscH in sys.h. | |

| #define | get_master_clock_frequency_low_part() (MAIN_FoscL) |

| Get low part of MAIN_Fosc defined as MAIN_FoscL in sys.h. | |

| #define | get_frequency_divider() (1 << (CLK_DIV & 0x07)) |

| Get master clock frequency divider (1 << CLK_DIV bits [0..2]) | |

| #define | get_frequency_divider_scale() (CLK_DIV & 0x07) |

| Get master clock frequency divider scale (CLK_DIV bits [0..2]) | |

| #define | set_frequency_divider_scale(divider_scale) |

| Update and get master clock frequency divider (CLK_DIV bits [0..2]) | |

| #define | enable_master_clock_output_div1() (CLK_DIV |= 0x40) |

| Enable master clock output. By default output set to P5.4 pin. | |

| #define | enable_master_clock_output_div2() (CLK_DIV |= 0x80) |

| Enable (master clock output)/2. By default output set to P5.4 pin. | |

| #define | enable_master_clock_output_div4() (CLK_DIV |= 0xC0) |

| Enable (master clock output)/4. By default output set to P5.4 pin. | |

| #define | disable_master_clock_output() (CLK_DIV &= 0x3f) |

| Disable master clock output. | |

| #define | get_master_clock_output_pin() ((CLK_DIV & 0xC0) == 0 ? NONE : (CLK_DIV & 0x08) == 0 ? P5_4 : P1_6) |

| Get master clock output. | |

| #define | set_master_clock_output_pin(pin) |

| Set master clock output pin. | |

Enumerations | |

| enum | master_clock_output_pin_t { NONE , P5_4 , P1_6 } |

| Master clock output pins enumeration. More... | |